热搜关键词: 遂宁主时钟 遂宁ptp模块 遂宁ptp板卡 遂宁ptp服务器

400-600-1588

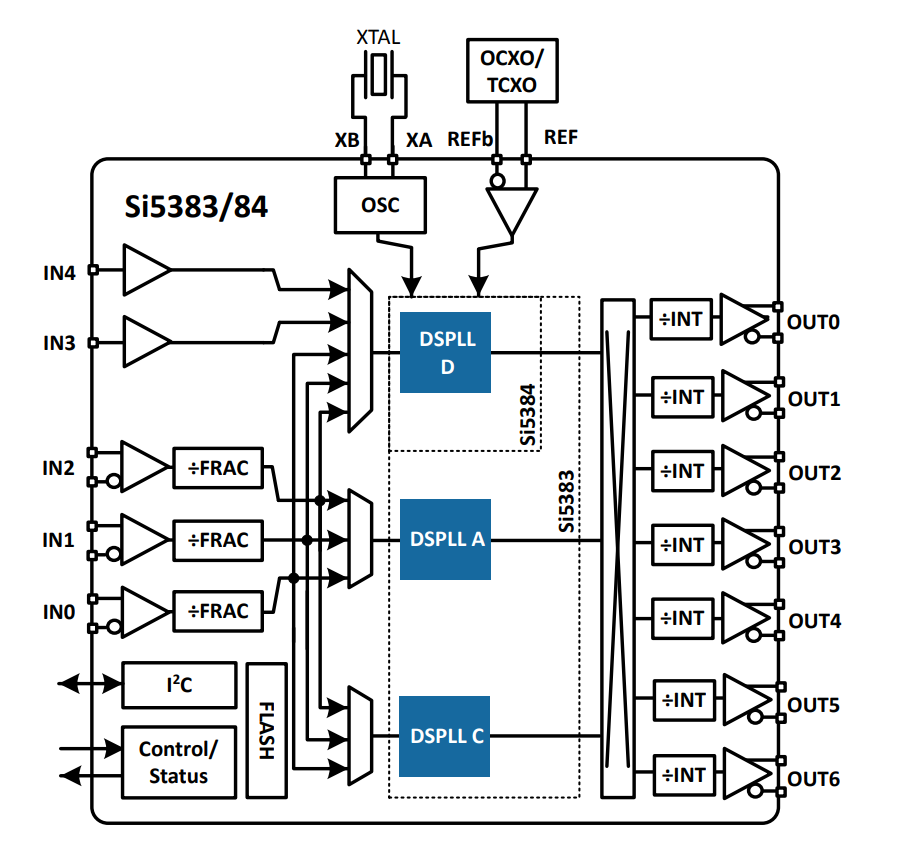

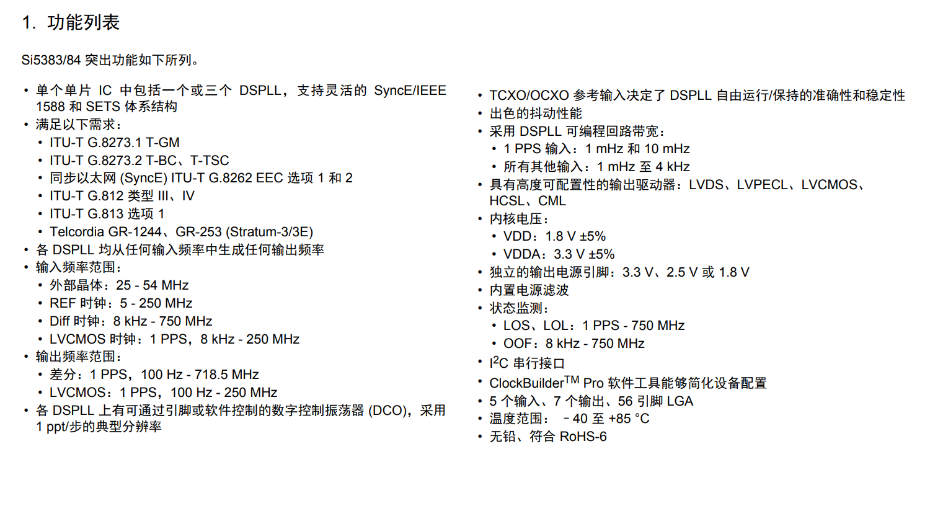

SI5383B-D00100-GM 时钟芯片支持 1 PPS 至 750 MHz 输入的网络同步时钟,Si5383/84 拥有业界更小尺寸和更低功耗的网络同步时钟,具备好频率合成灵活性和低抖动。 Si5383/84 非常适合无线回程、IP 无线电、小型宏单元通信系统以及需要传统网络同步和基于数据包的网络同步的数据中心交换机。 三种独立的 DSPLL 可分别配置为 SyncE PLL、IEEE 1588 DCO 或通用 PLL,适用于处理器/FPGA 时钟。Si5383/84 还可用于需要 Stratum 3/3E 合规的旧式 SETS 系统。此外,DSPLL D 上可锁定 1 PPS 输入频率。DCO 模式提供兆分之一 (ppt) 的高精度定时调整。Si5383/84 设计有自己的特点,允许设备通过 广泛的频率范围接收 TCXO/OCXO 参考,参考时钟抖动不会降低输出性能。可通过串行接口对 Si5383/84 进行配置,还可使用 ClockBuilder Pro 软件对 Si5383/84 轻松编程。此外,还提供工厂预 编程设备。

主要特点

• 单个单片 IC 中包括一个或三个单独的 DSPLL,支持灵活的 SyncE/IEEE 1588 和 SETS 体系结构

• 输入频率范围:

• 外部晶体:25 - 54 MHz

• REF 时钟:5 - 250 MHz

• Diff 时钟:8 kHz - 750 MHz

• LVCMOS 时钟:1 PPS,8 kHz - 250 MHz

• 输出频率范围:

• 差分:1 PPS,100 Hz - 718.5 MHz

• LVCMOS:1 PPS,100 Hz - 250 MHz

• 不到 150 fs 的低抖动

应用

• 同步以太网 (SyncE) ITU-T G.8262 EEC 选项 1 和 2

• 电信大主时钟 (T-GM),由 ITU-T G.8273.1 定义

• 电信边界时钟和从时钟(T-BC,T-TSC),由 ITU-T G.8273.2 定义

• IEEE 1588 (PTP) 从时钟同步

• Stratum 3/3E、G.812, G.813、GR-1244、GR-253 网络同步

• 1 Hz/1 PPS 时钟倍频器